EVG805键合机原理

半导体器件的垂直堆叠已经成为使器件密度和性能不断提高的日益可行的方法。晶圆间键合是实现3D堆叠设备的重要工艺步骤。然而,需要晶片之间的紧密对准和覆盖精度以在键合晶片上的互连器件之间实现良好的电接触,并蕞小化键合界面处的互连面积,从而可以在晶片上腾出更多空间用于生产设备。支持组件路线图所需的间距不断减小,这推动了每一代新产品的更严格的晶圆间键合规范。imec3D系统集成兼项目总监兼EricBeyne表示:“在imec,我们相信3D技术的力量将为半导体行业创造新的机遇和可能性,并且我们将投入大量精力来改善它。“特别关注的领域是晶圆对晶圆的键合,在这一方面,我们通过与EVGroup等行业合作伙伴的合作取得了优异的成绩。去年,我们成功地缩短了芯片连接之间的距离或间距,将晶圆间的混合键合厚度减小到1.4微米,是目前业界标准间距的四倍。今年,我们正在努力将间距至少降低一半。” EVG键合机的键合室配有通用键合盖,可快速排空,快速加热和冷却。EVG805键合机原理

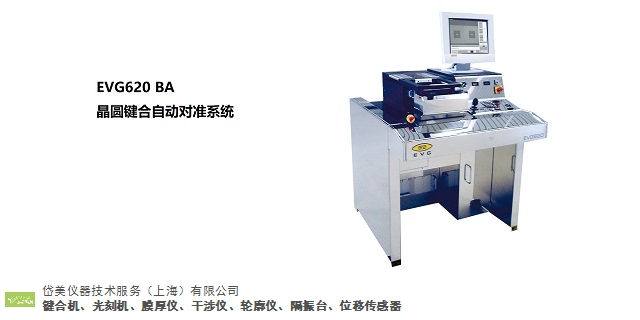

晶圆级封装的实现可以带来许多经济利益。它允许晶圆制造,封装和测试的集成,从而简化制造过程。缩短的制造周期时间可提高生产量并降低每单位制造成本。晶圆级封装还可以减小封装尺寸,从而节省材料并进一步降低生产成本。然而,更重要的是,减小的封装尺寸允许组件用于更广范的高级产品中。晶圆级封装的主要市场驱动因素之一是需要更小的组件尺寸,尤其是减小封装高度。岱美仪器提供的EVG的晶圆键合机,可以实现晶圆级封装的功能。 EVG520键合机免税价格晶圆键合机(系统)EVG®510 ,拥有150、200mm晶圆单腔系统 ;拥有EVG®501 键合机所有功能。

表面带有微结构硅晶圆的界面已受到极大的损伤,其表面粗糙度远高于抛光硅片( Ra < 0. 5 nm) ,有时甚至可以达到 1 μm 以上。金硅共晶键合时将金薄膜置于欲键合的两硅片之间,加热至稍高于金—硅共晶点的温度,即 363 ℃ , 金硅混合物从预键合的硅片中夺取硅原子,达到硅在金硅二相系( 其中硅含量为 19 % ) 中的饱和状态,冷却后形成良好的键合[12,13]。而光刻、深刻蚀、清洗等工艺带来的杂质对于金硅二相系的形成有很大的影响。以表面粗糙度极高且有杂质的硅晶圆完成键合,达到既定的键合质量成为研究重点。

EVG®850SOI的自动化生产键合系统 自动化生产键合系统,适用于多种熔融/分子晶圆键合应用 特色 技术数据 SOI晶片是微电子行业有望生产出更快,性能更高的微电子设备的有希望的新基础材料。晶圆键合技术是SOI晶圆制造工艺的一项关键技术,可在绝缘基板上实现高质量的单晶硅膜。借助EVG850 SOI生产键合系统,SOI键合的所有基本步骤-从清洁和对准到预键合和红外检查-都结合了起来。因此,EVG850确保了高达300mm尺寸的无空隙SOI晶片的高产量生产工艺。EVG850是wei一在高通量,高产量环境下运行的生产系统,已被确立为SOI晶圆市场的行业标准。EVG所有键合机系统都可以通过远程通信。

共晶键合[8,9]是利用某些共晶合金熔融温度较低的特点,以其作为中间键合介质层,通过加热熔融产生金属—半导体共晶相来实现。因此,中间介质层的选取可以很大程度影响共晶键合的工艺以及键合质量。中间金属键合介质层种类很多,通常有铝、金、钛、铬、铅—锡等。虽然金—硅共熔温度不是蕞 低( 363 ℃ ) 的,但其共晶体的一种成分即为预键合材料硅本身,可以降低键合工艺难度,且其液相粘结性好,故本文采用金—硅合金共晶相作为中间键合介质层进 行表面有微结构的硅—硅共晶键合技术的研究。而金层与 硅衬底的结合力较弱,故还要加入钛金属作为黏结层增强金层与硅衬底的结合力,同时钛也具有阻挡扩散层的作用, 可以阻止金向硅中扩散[10,11]。 我们在不需重新配置硬件的情况下,EVG键合机可以在真空下执行SOI / SDB(硅的直接键合)预键合。贵州键合机质保期多久

EVG的GEMINI系列是自动化生产晶圆键合系统。EVG805键合机原理

长久键合系统 EVG晶圆键合方法的引入将键合对准与键合步骤分离开来,立即在业内掀起了市场geming。利用高温和受控气体环境下的高接触力,这种新颖的方法已成为当今的工艺标准,EVG的键合机设备占据了半自动和全自动晶圆键合机的主要市场份额,并且安装的机台已经超过1500个。EVG的晶圆键合机可提供蕞/佳的总拥有成本(TCO),并具有多种设计功能,可优化键合良率。针对MEMS,3D集成或gao级封装的不同市场需求,EVG优化了用于对准的多个模块。下面是EVG的键合机EVG500系列介绍。 EVG805键合机原理

上一篇: 四川EVG850 LT键合机

下一篇: 临时键合键合机可以试用吗