孝感高速PCB制板原理

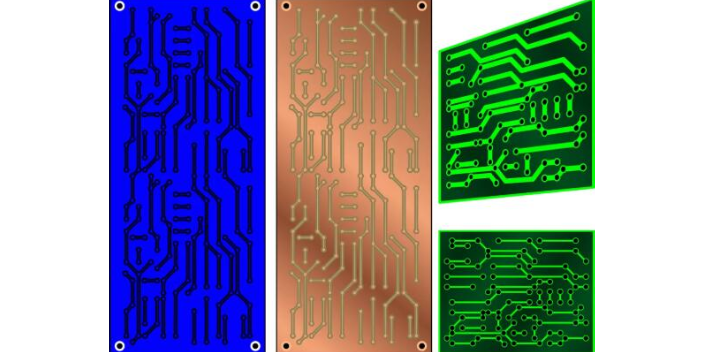

PCB制板生产中的标志点设计必须在板的长边对角线上有一个与整板定位相对应的标志点,在板上集成电路引脚中心距小于0.65mm的集成电路长边对角线上有一对与芯片定位相对应的标志点;当pcb两面都有贴片时,按此规则标记pcb两面。2.PCB边缘应留有5mm的工艺边(机夹PCB的比较小间距要求),IC引脚中心距小于0.65mm的芯片距板边(含工艺边)应大于13mm板的四个角用ф5圆弧倒角。Pcb要拼接。考虑到目前pcb翼弯程度,比较好拼接长度在200mm左右(设备加工尺寸:最大长度330mm;最大宽度250mm),并且尽量不要在宽度方向拼,防止制作过程中弯曲。层压是抑制PCB制板电磁干扰的重要手段。孝感高速PCB制板原理

PCB中过孔的作用在高速PCB设计中,在双面板和多层板设计时,为连通各层之间的印制导线,在连接处需要打一个孔将各层走线进行连接。该孔即为过孔。垂直过孔是常见的形式互连传输线连接。过孔被分为三类:通孔、盲孔和埋孔。一、通孔:是将板子打通。二、盲、埋孔。京晓科技可提供2-60层PCB设计服务,对HDI盲埋孔、工控医疗类、高速通讯类,消费电子类,航空航天类,电源板,射频板有丰富设计经验。阻抗设计,叠层设计,生产制造,EQ确认等问题,一对一全程服务。京晓科技致力于提供高性价比的PCB产品服务,打造从PCB设计、PCB生产到SMT贴片的一站式服务生态体。孝感生产PCB制板走线PCB制板的种类、柔性。

PCB制板表面涂层技术PCB表面涂层技术是指除阻焊涂层(和保护层)以外的用于电气连接的可焊性涂层(电镀)和保护层。按用途分类:1.焊接:因为铜的表面必须有涂层保护,否则在空气中很容易被氧化。2.连接器:电镀镍/金或化学镀镍/金(硬金,含有磷和钴)3.用于引线键合的引线键合工艺。热风整平(HASL或哈尔)热空气(230℃)压平熔融Sn/Pb焊料PCB的方法。1.基本要求:(1).锡/铅=63/37(重量比)(2)涂层厚度应至少大于3um。(3)避免因锡含量不足而形成不可焊的Cu3Sn。比如Sn/Pb合金镀层太薄,焊点由可焊的cu6sn5-cu4sn3-Cu3Sn2—-不可焊的Cu3Sn组成。2.工艺流程去除抗蚀剂-清洗板面-印刷阻焊层和字符-清洗-涂布助焊剂-热风整平-清洗。3.缺点:A.铅和锡的表面张力过大,容易形成龟背现象。B.焊盘的不平坦表面不利于SMT焊接。化学镀Ni/Au是指在PCB连接焊盘上先化学镀镍(厚度≥3um),再镀一层0.05-0.15um的薄层金或一层0.3-0.5um的厚层金。由于化学镀层均匀、共面性好,并能提供多种焊接性能,因此具有推广应用的趋势。薄镀金(0.05-0.1μm)用于保护Ni的可焊性,而厚镀金(0.3-0.5μm)用于引线键合。

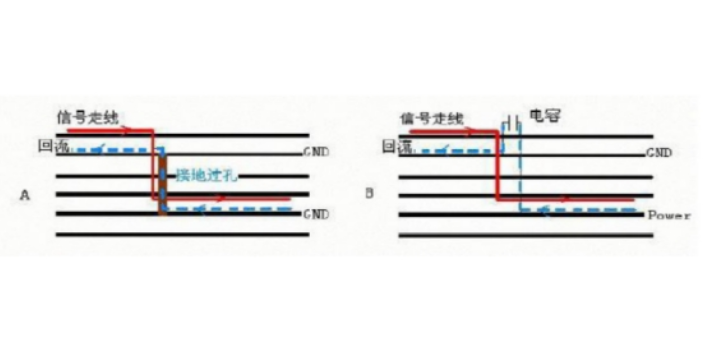

PCB制板设计中的ESD抑制PCB布线是ESD保护的关键要素。合理的PCB设计可以减少因故障检查和返工带来的不必要的成本。在PCB设计中,瞬态电压抑制器(TVS)二极管用于抑制ESD放电引起的直接电荷注入,因此在PCB设计中克服放电电流引起的电磁干扰(EMI)效应更为重要。本文将提供可以优化ESD保护的PCB设计标准。1.环路电流被感应到闭合的磁通变化的回路中。电流的幅度与环的面积成正比。更大的回路包含更多的磁通量,因此在回路中感应出更强的电流。因此,必须减少回路面积。很常见的环路是由电源和地形成的。如果可能,可以采用带电源和接地层的多层PCB设计。多层电路板不仅小化了电源和地之间的回路面积,还减少了ESD脉冲产生的高频EMI电磁场。如果不能使用多层电路板,则用于供电和接地的导线必须以网格形状连接。并网可以起到电源和接地层的作用。每层的印刷线路通过过孔连接,过孔连接间隔在每个方向都要在6cm以内。此外,在布线时,可以通过使电源和接地印刷电路尽量靠近来减少回路面积。合理的PCB制板设计可以减少因故障检查和返工带来的不必要的成本。

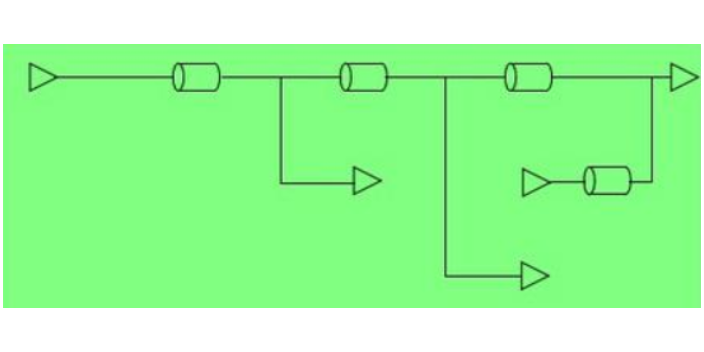

SDRAM的端接1、时钟采用∏型(RCR)滤波,∏型滤波的布局要紧凑,布线时不要形成Stub。2、控制总线、地址总线采用在源端串接电阻或者直连。3、数据线有两种端接方法,一种是在CPU和SDRAM中间串接电阻,另一种是分别在CPU和SDRAM两端串接电阻,具体的情况可以根据仿真确定。京晓科技可提供2-60层PCB设计服务,对HDI盲埋孔、工控医疗类、高速通讯类,消费电子类,航空航天类,电源板,射频板有丰富设计经验。阻抗设计,叠层设计,生产制造,EQ确认等问题,一对一全程服务。京晓科技致力于提供高性价比的PCB产品服务,打造从PCB设计、PCB生产到SMT贴片的一站式服务生态体。印制PCB制板的尺寸与器件的配置。宜昌专业PCB制板哪家好

PCB制板制作过程中容易发生的问题。孝感高速PCB制板原理

差分走线及等长注意事项1.阻抗匹配的情况下,间距越小越好2.蛇状线<圆弧转角<45度转角<90度转角(等长危害程度)蛇状线的危害比转角小一些,因此若空间许可,尽量用蛇状线代替转角,来达成等长的目的。3.圆弧转角<45度转角<90度转角(走线转角危害程度)转角所造成的相位差,以90度转角大,45度转角次之,圆滑转角小。圆滑转角所产生的共模噪声比90度转角小。4.等长优先级大于间距间距<长度差分讯号不等长,会造成逻辑判断错误,而间距不固定对逻辑判断的影响,几乎是微乎其微。而阻抗方面,间距不固定虽然会有变化,但其变化通常10%以内,只相当于一个过孔的影响。至于EMI幅射干扰的增加,与抗干扰能力的下降,可在间距变化之处,用GNDFill技巧,并多打过孔直接连到MainGND,以减少EMI幅射干扰,以及被动干扰的机会[29-30]。如前述,差分讯号重要的就是要等长,因此若无法兼顾固定间距与等长,则需以等长为优先考虑。孝感高速PCB制板原理

上一篇: 黄石专业PCB制版布线

下一篇: 十堰了解PCB制板走线